硬件设计

重要

以下内容仅适用于 HT32 M0p & HT32 M3 系列芯片,HT32 M4 可参考 PCB Layout 。

关于 HT32 的硬件设计,可先参考官网 Application Notes 的 《HT32 MCU 硬件开发指南》

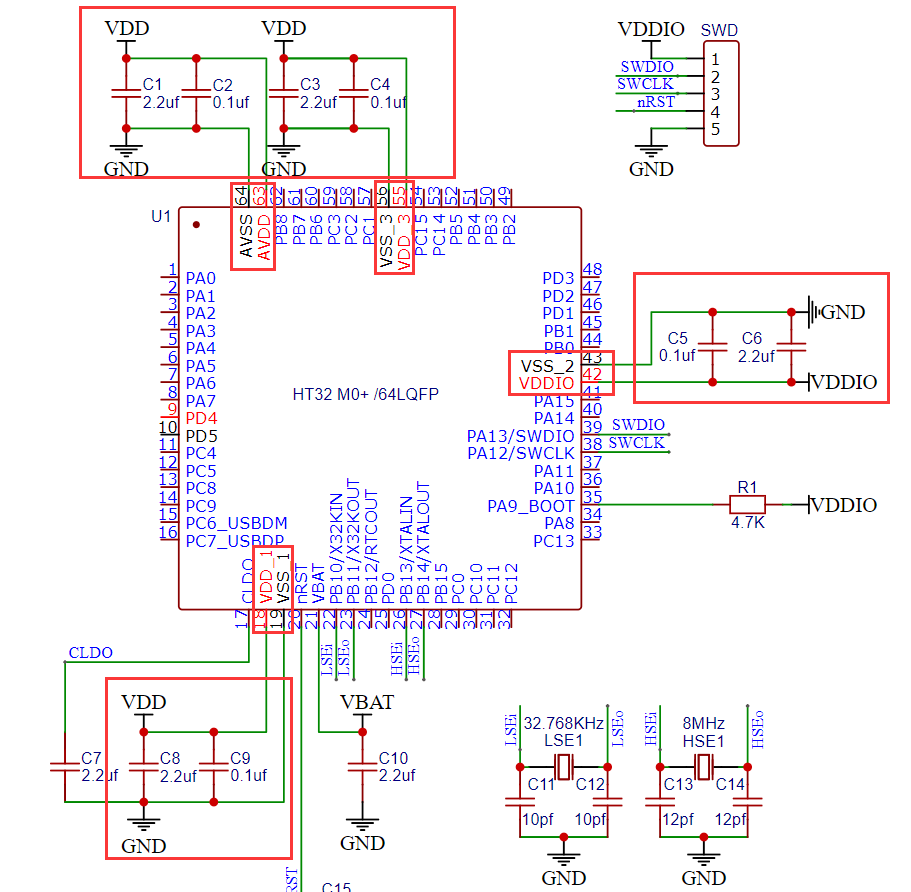

最小系统原理图

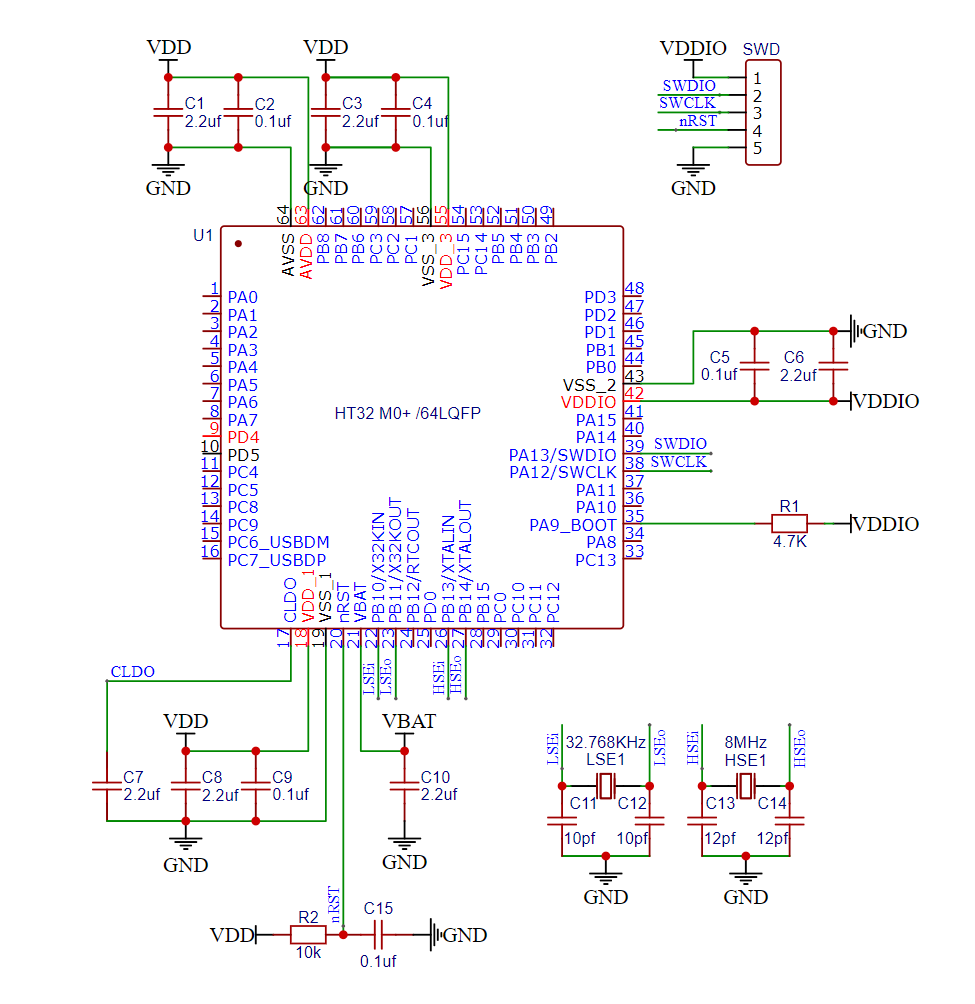

HT32 M0+ 最小系统范例

HT32 M0+ 最小系统

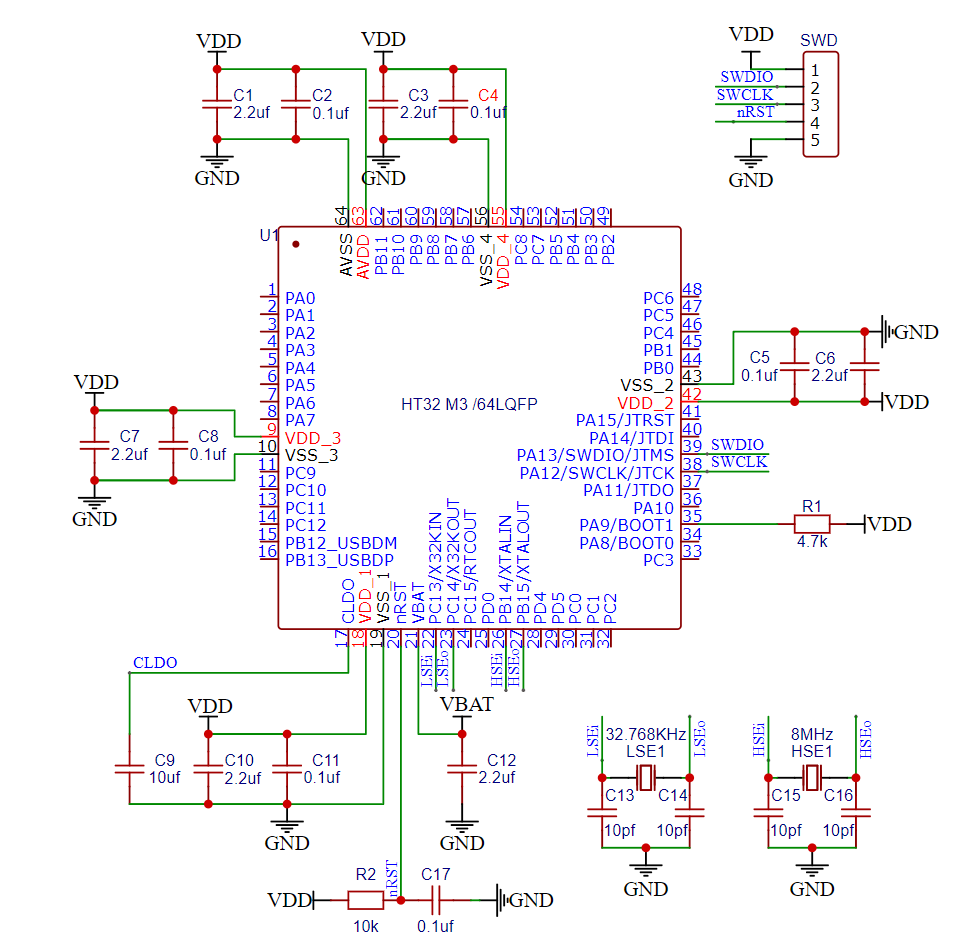

HT32 M3 最小系统范例

HT32 M3 最小系统

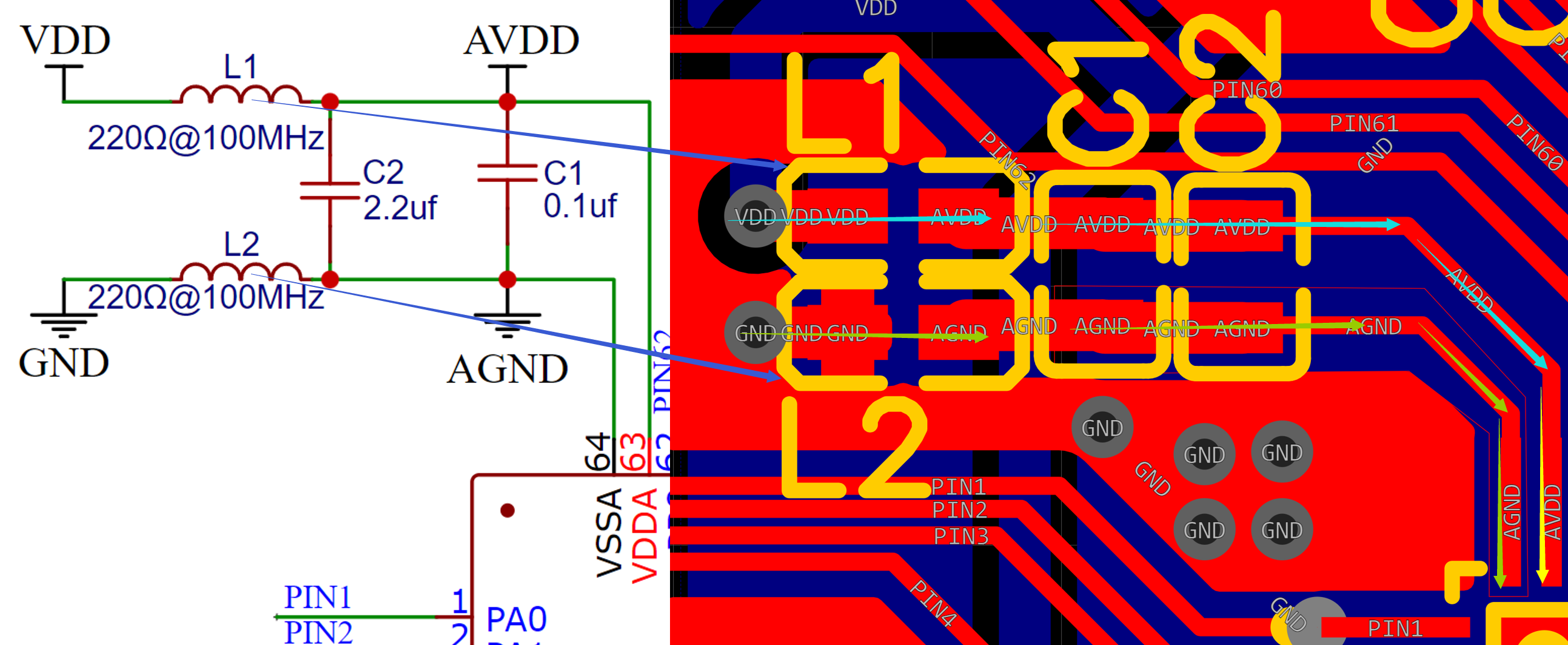

电源电路设计

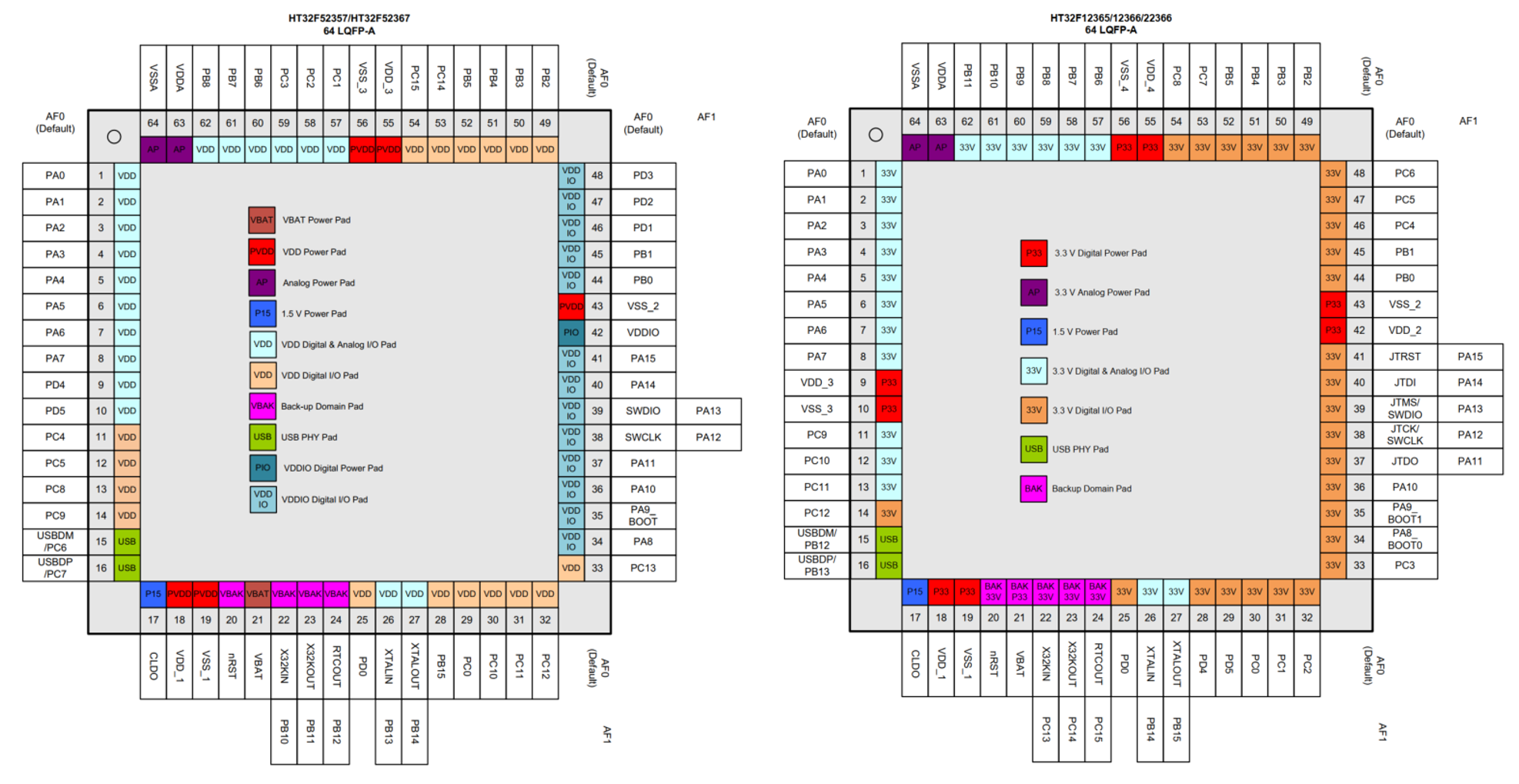

HT32 M0+/M3 有多个供电电源端口,在 引脚图 中的图块,可看到 GPIO 不同颜色图块对应的电源域。

VDD_n & VSS_n : 数字 I/O 电压

CLDO / ULDO :内核 LDO 1.5 V 输出电源

AVDD & AVSS : 模拟(ADC CMP …) 电压

VDDIO & VSS_2 : 部分 数字 I/O 电压

VBAT : 备份域的电池电源,仅部分 HT32 提供。

VLCD : LCD 电源电压 , 仅 LCD 系列 HT32F57xxx 提供。

HT32 引脚图

具体请参考型号对应的 HT32Fxxxxx_Datasheet.pdf 内 引脚图 章节。

重要

VDDIO 和 VDD 电压无关联,VDDIO 供电电压不受 VDD 电压限制。

VDDIO 可使用 其他 IC-VDD 电压,对应的GPIO可作为电压匹配的接口使用,如通讯接口。

并非所有型号都有 VDDIO 功能。

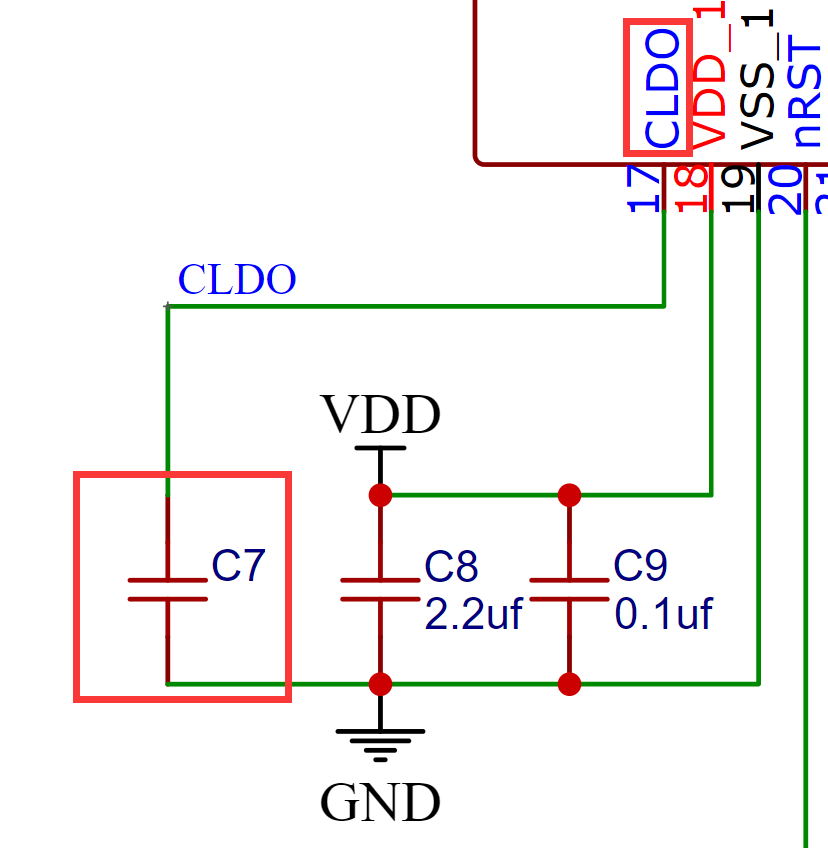

1. CLDO / ULDO

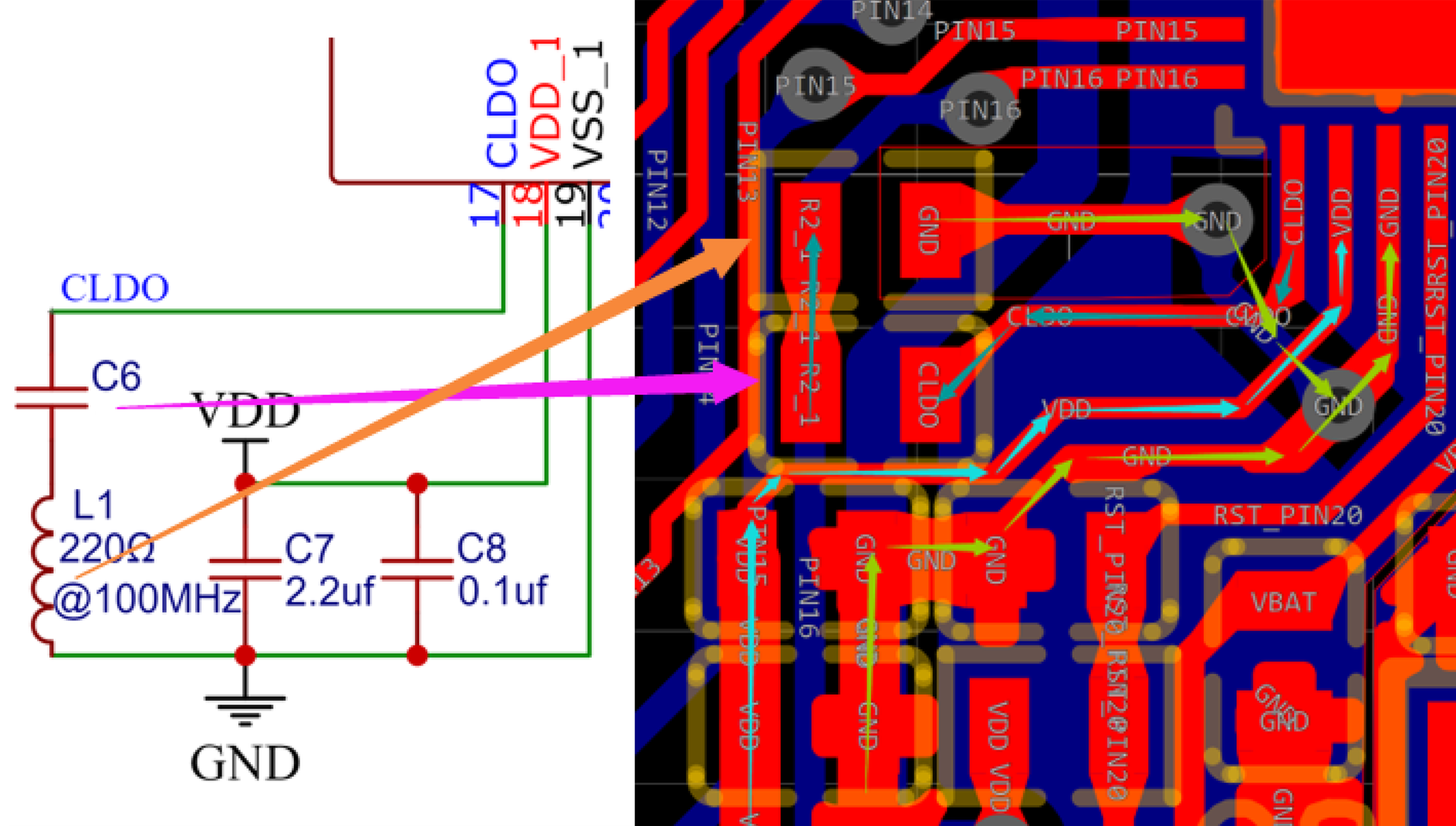

Schematic

HT32 M0+/M3 的 CLDO/ULDO 需要外接电容,需要的电容材质和容值参考 CLDO/ULDO说明 。

HT32_SCH_CLDO

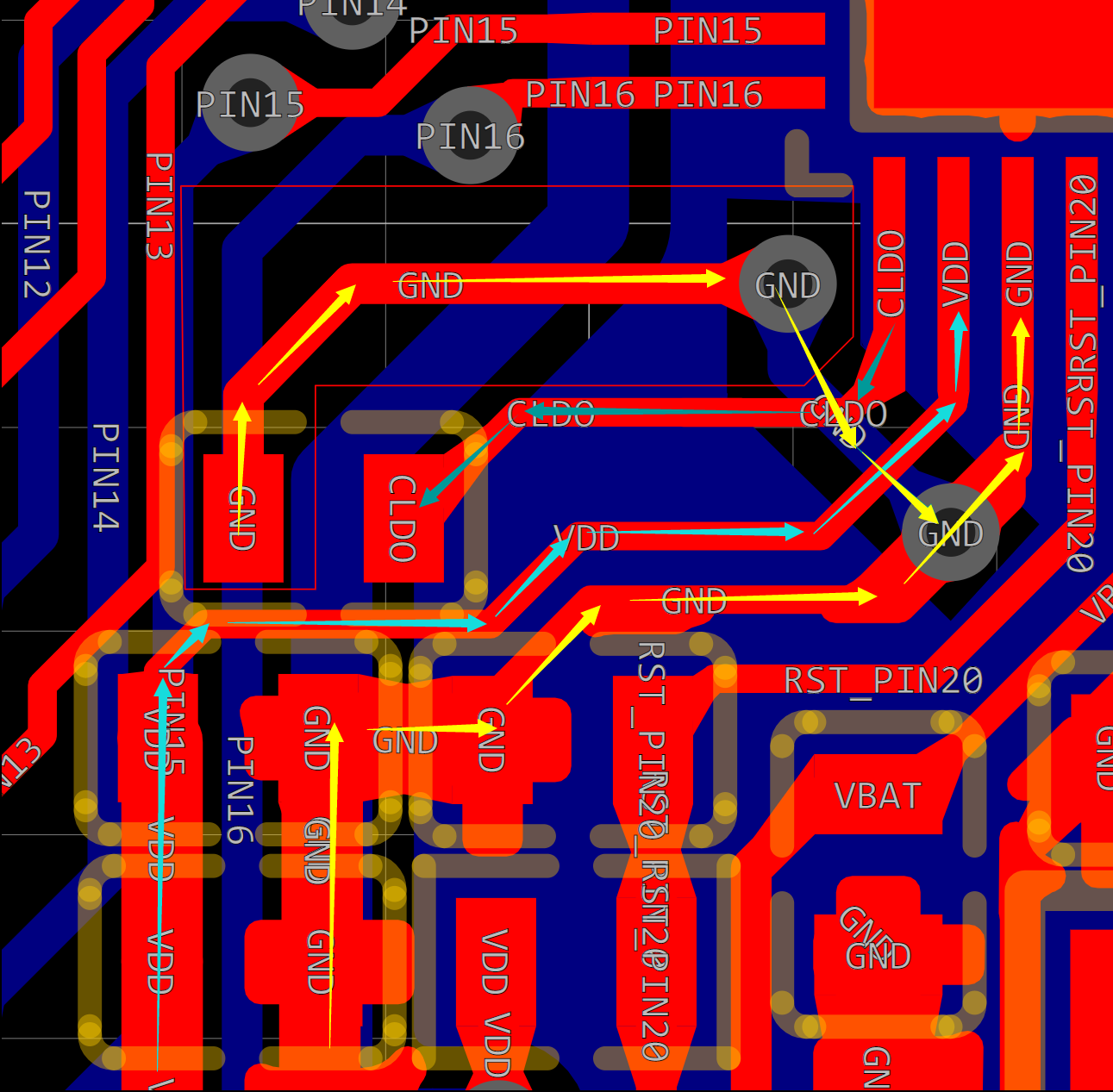

PCB Layout

外接电容 位置尽量靠近 CLDO 与 VSS_1 引脚。

外接电容 负极应优先回流 VSS_1。

铺铜 时, 外接电容 负极走线,不能混入 铺铜(GND) ,即 外接电容 负极走线 需要和 铺铜 (GND)隔离。

HT32_PCB_CLDO

警告

外接电容 负极应优先回流 VSS_1,负极走线 和 铺铜(GND) 隔离,可大幅增加 HT32 抗干扰能力。

如产品需要通过 EMC ,可在 CLDO/ULDO 外接电容后,再串联一个磁珠,磁珠推荐 220Ω@100MHz,且磁珠负极优先回流 VSS_1,负极走线 和 铺铜 隔离。

HT32_CLDO 增加磁珠

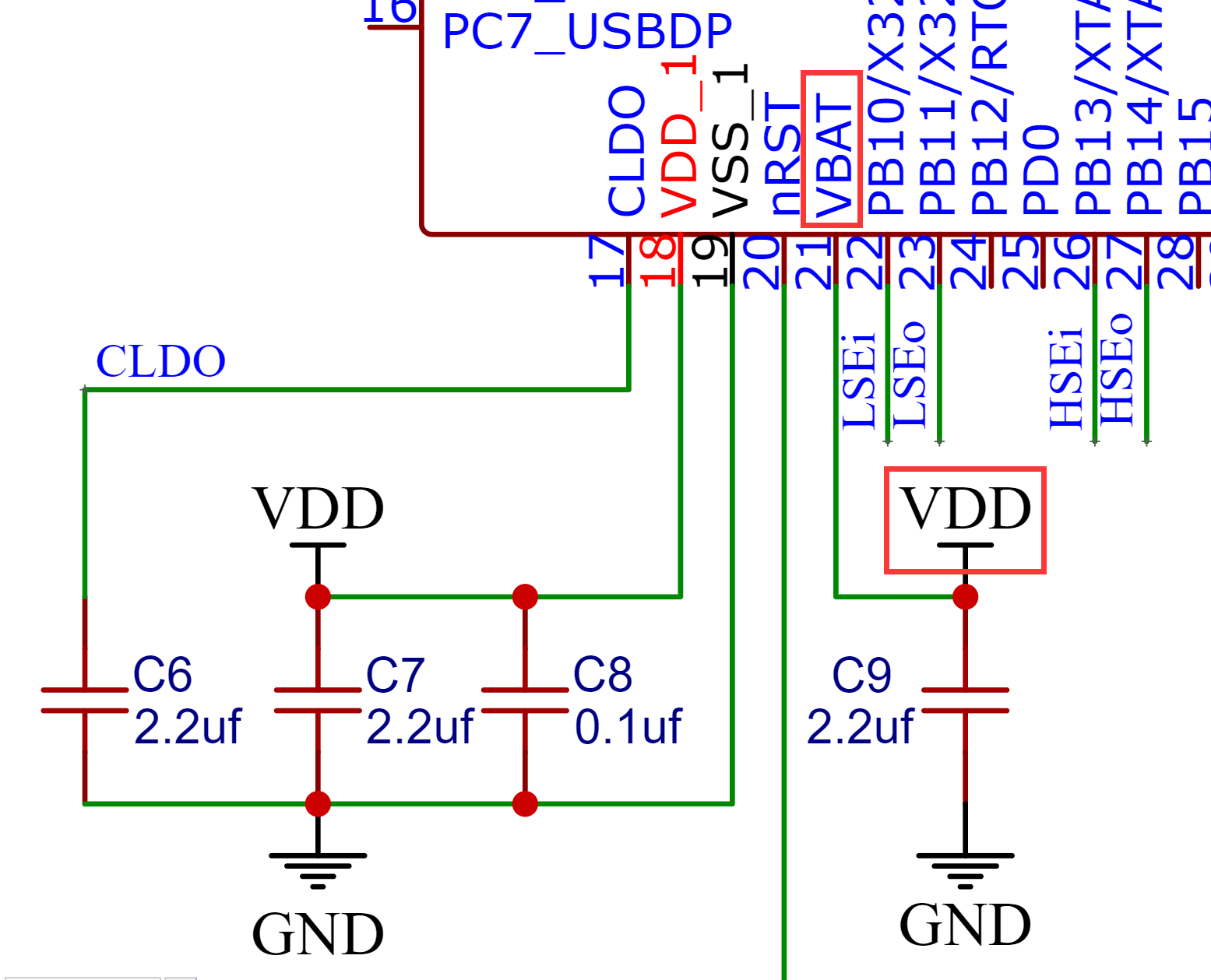

2. VDD / AVDD / VDDIO

Schematic

VDD_1 & VSS_1 , AVDD & AVSS 的 滤波电容**必须使用 **大+小组合 ,推荐 10uF/2.2uF + 0.1uF 。

其他 VDD_n/VDDIO & VSS_n 的 滤波电容,建议使用 大+小组合 ,推荐同上;如需精简, 滤波电容 也至少需要 小电容 ,推荐 0.1uF 。

HT32_SCH_VDD

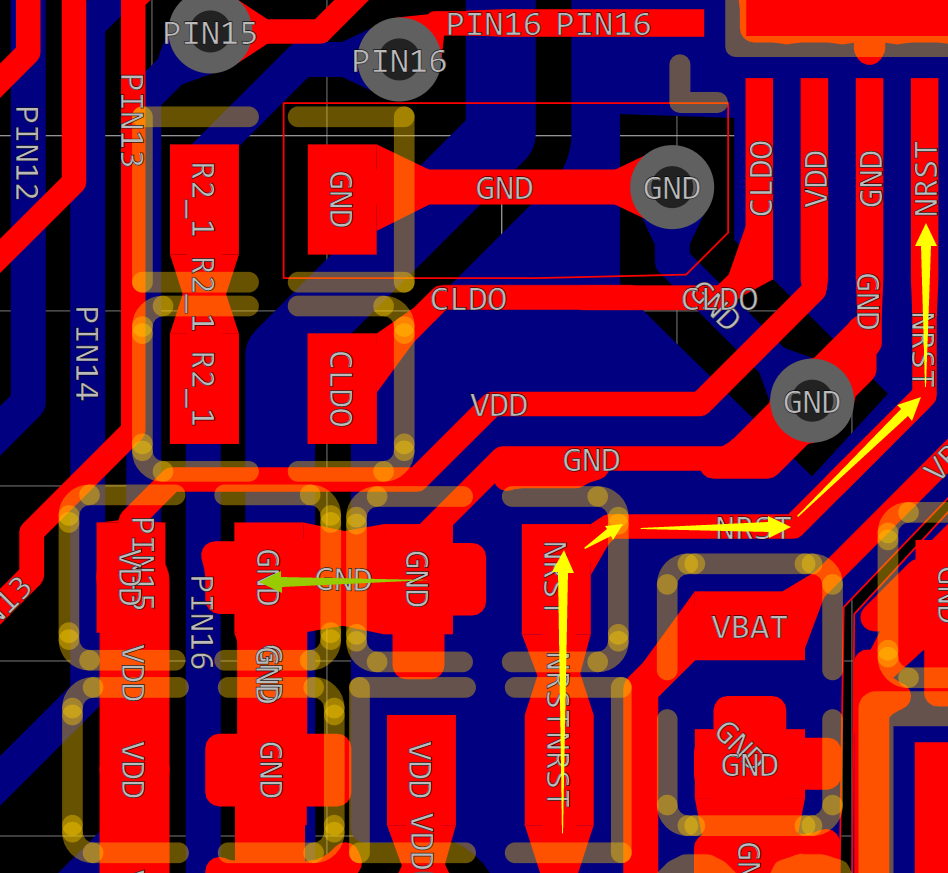

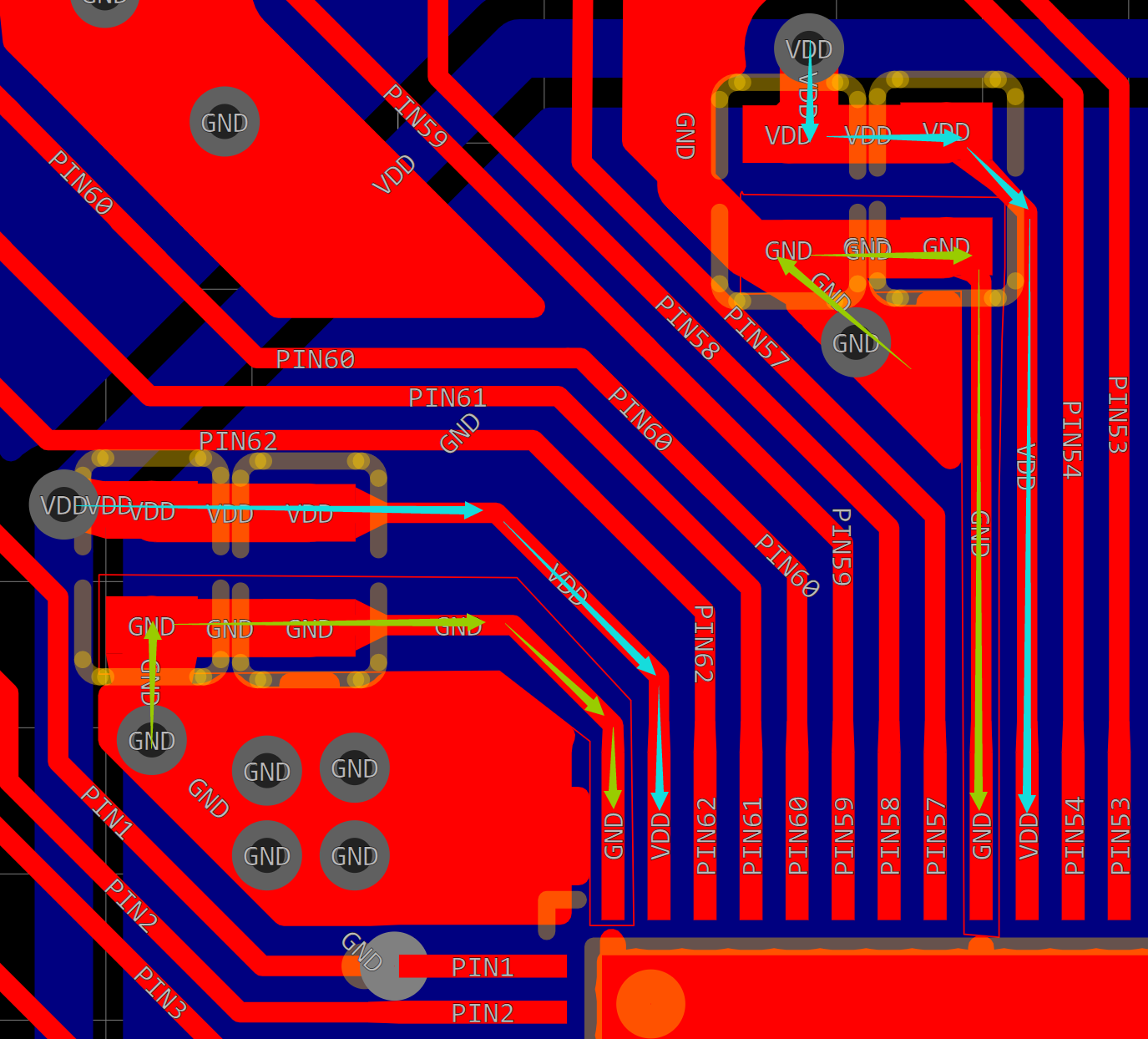

PCB Layout

滤波电容 位置尽量靠近对应的 电源引脚 ,且 小电容 优先靠近 电源引脚。

VDD & VSS 走线,需先经过 滤波电容 再接入 VDD & VSS 引脚,且不再引出供 HT32 其他供电引脚和其他电路使用。

铺铜 时,请遵循上一条原则,走线不能混入 铺铜(GND), 即 VDD & VSS 走线需要和 铺铜 隔离。

VDD & VSS 走线 或 铺铜 时,要避开大电流或功率器件的回流路径。

HT32_PCB_VDD

警告

此 MCU 供电端口 PCB Layout 原则,有普适性,适合大部分 MCU 供电端口的电源设计。

如 AVDD & AVSS 干扰严重会影响 ADC 采样,可以在 AVDD 或 AVDD & AVSS 电容前串联磁珠提高抗干扰能力,磁珠推荐 220Ω@100MHz。

HT32_PCB_AVDD

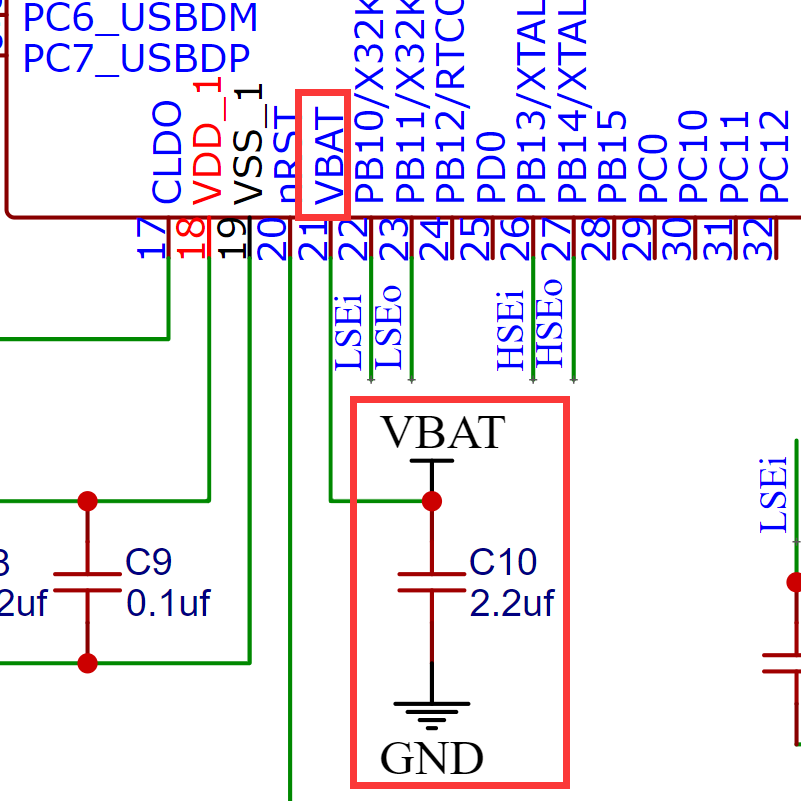

3. VBAT / VLCD

PCB Layout

可参考 VDD PCB Layout 。

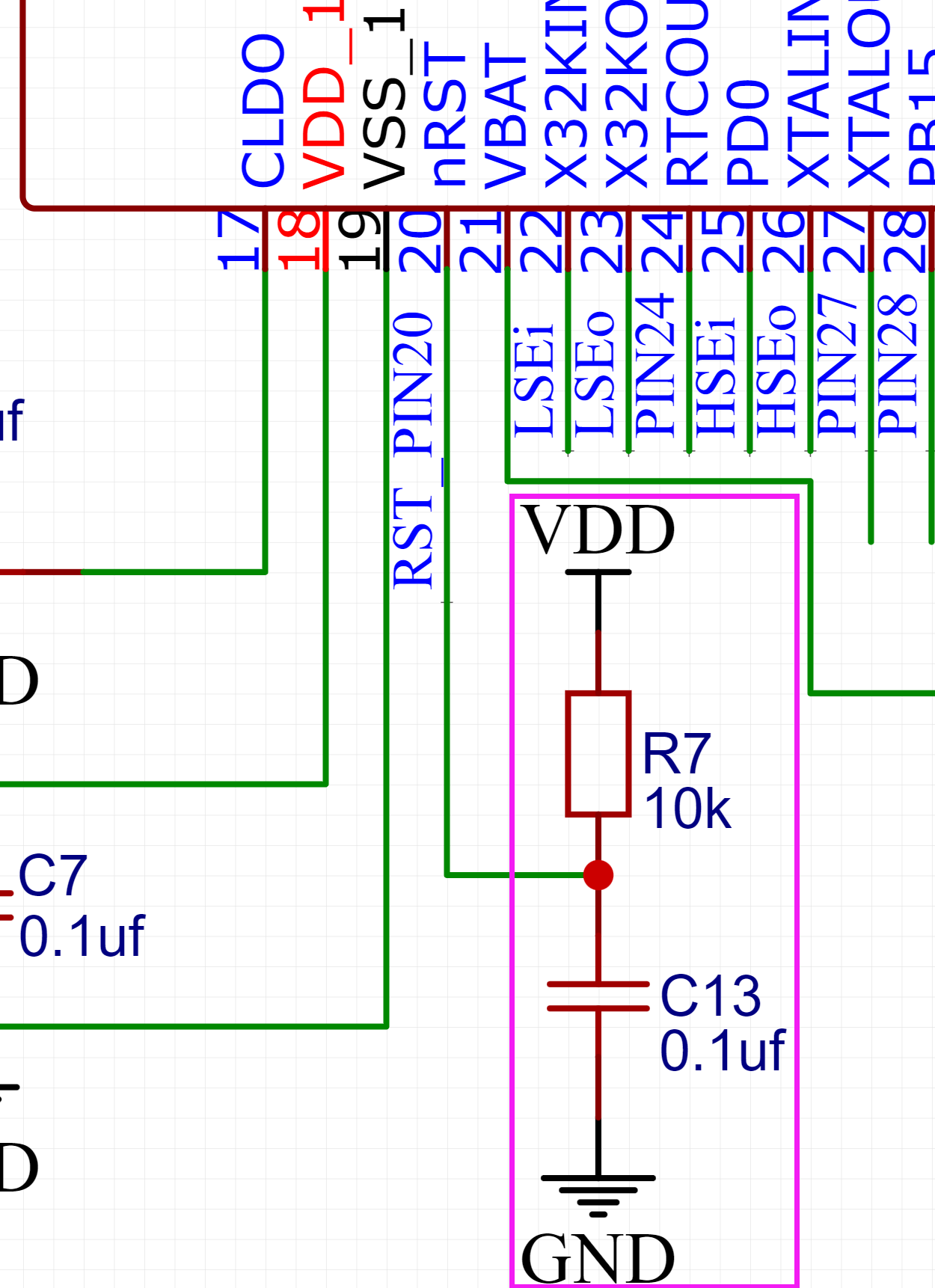

复位电路设计

nRST

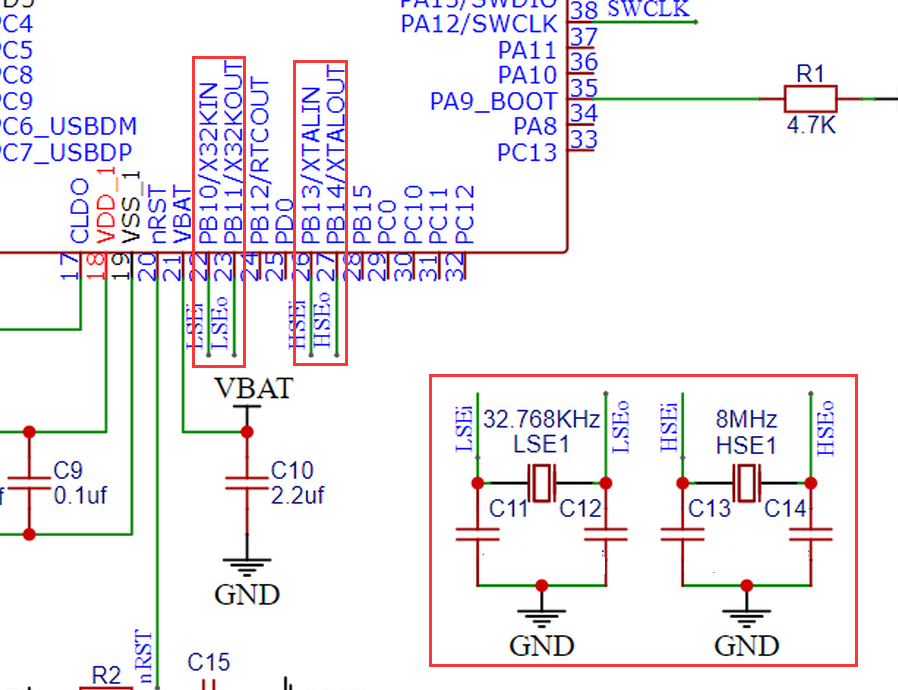

晶振电路设计

HSE / LSE

Schematic

外部高速晶振 HSE :

HT32F40xxx 系列 HSE = 20MHz ;

HT32F40xxx 系列 HSE = 4~16MHz,推荐使用 8MHz。

外部低速晶振 LSE : 通常为 32.768KHz ;

HSE 和 LSE 的 晶振规格 和 负载电容 需根据HT32型号选择。

HT32_SCH_XTAL

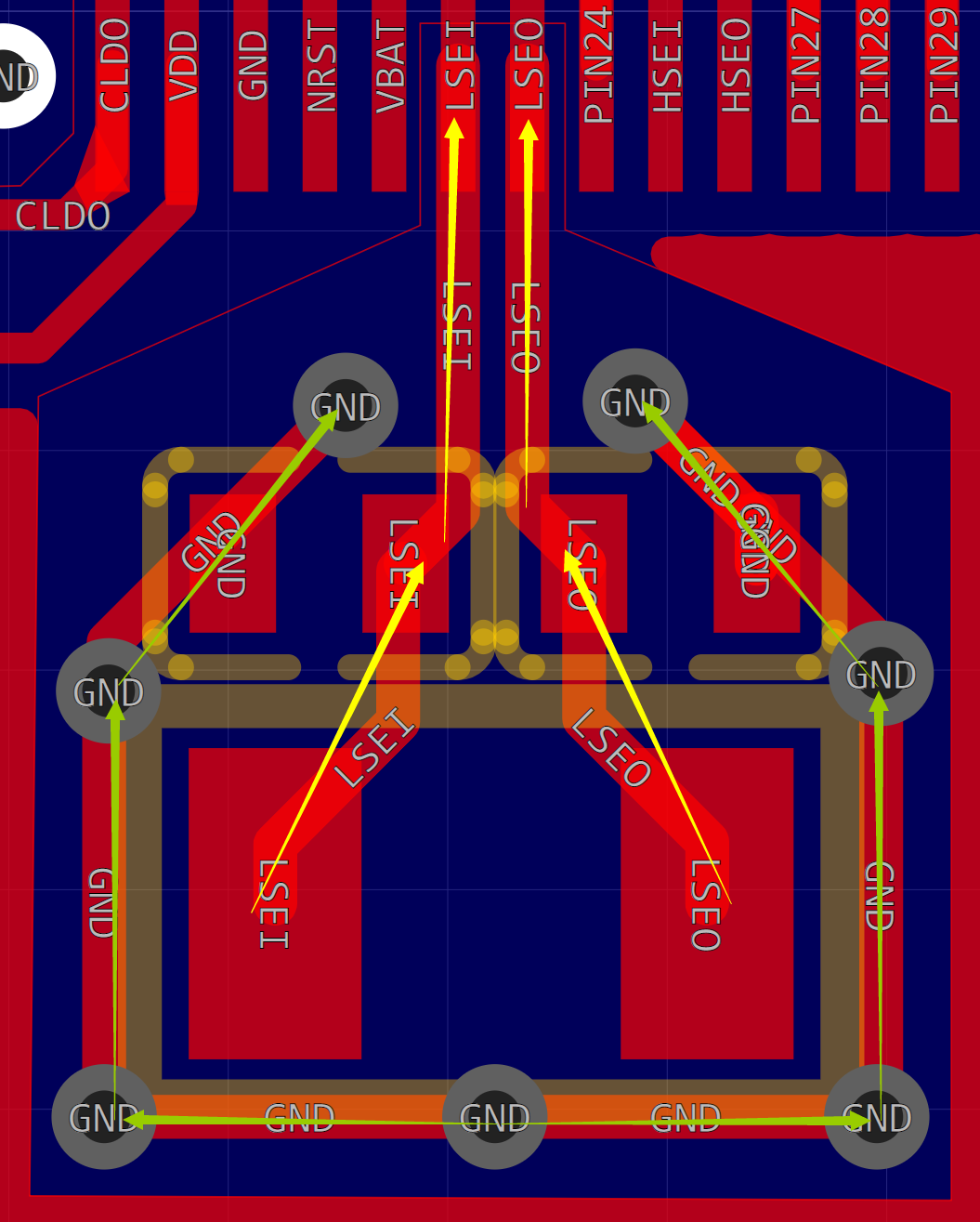

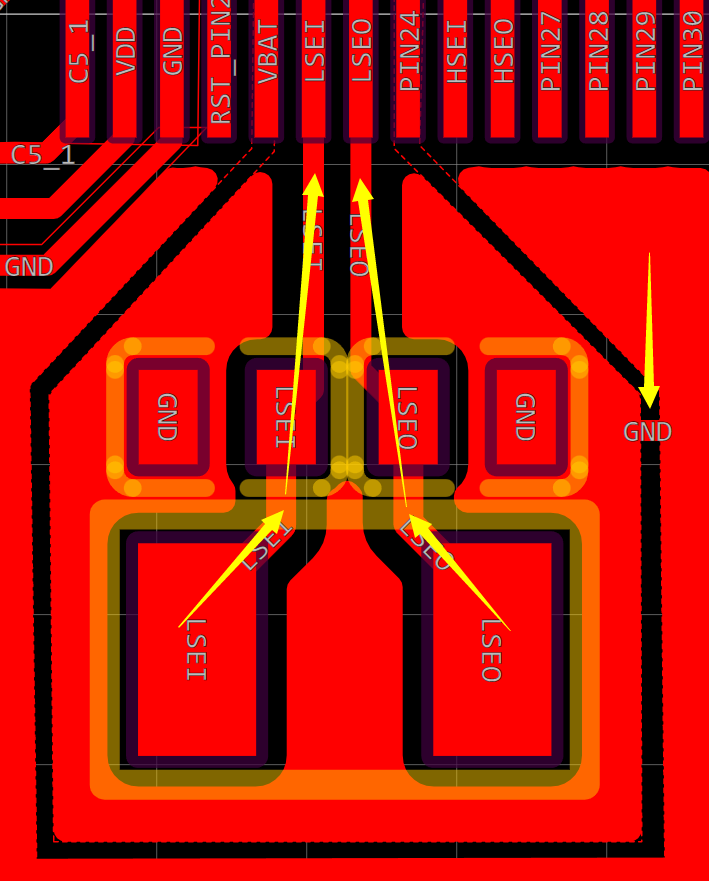

PCB Layout

晶振 走线尽量短,避免走线过长,导致 晶振 产生 寄生电感,影响 晶振 性能。

晶振 顶层地走线环绕包裹晶振区域,并增加过孔连接到底层;

晶振 区域内(所有层)不能有其他走线,以免互相干扰;

晶振 顶层(和中间层)区域 不铺铜(GND) 或 分割铺铜(GND),底层必须 铺铜(GND)。

如是 单层PCB , 晶振 顶层区域 分割铺铜(GND) ,并单点走线和 铺铜(GND) 连接。

HT32_PCB_XTAL 双/多层

HT32_PCB_XTAL 单层

警告

HSE 和 LSE 的 负载电容 有 最大值 和 最小值 有限制;

HSE 和 LSE 的 晶振规格 的 等效串联电阻 有限制;

一定要参考型号对应的

HT32Fxxxxx_Datasheet.pdf内 外部时钟特性 章节。HSE 和 LSE Layout 原则,有普适性,适合大部分 MCU 外部晶振电路的电源设计。

如产品需要通过 EMC,则建议用此 Layout 方法,可提高 EMC 性能。

关于 HT32 的晶振设计,可先参考官网 Application Notes 的 《HT32 系列单片机晶振&ADC 设计的注意事项及 PCB 布局指南》

内置预驱(Gate-Drive)

TODO

其他走线

TODO